MOSFETの動作原理

MOSFETは動作モードによりエンハンスメント型とデプレッション型に分けられます。エンハンスメント型とは、バイアス電圧が印加されておらず、電圧が印加されていないときの MOSFET を指します。誘導チャネル。デプレッション型とは、バイアス電圧が印加されていないときの MOSFET を指します。導電チャネルが表示されます。

実際のアプリケーションでは、MOSFET は N チャネル エンハンスメント型と P チャネル エンハンスメント型のみです。 NMOSFETはオン抵抗が小さく製造が容易なため、実際のアプリケーションではPMOSよりもNMOSの方が一般的です。

エンハンスメントモードMOSFET

エンハンスメント モード MOSFET のドレイン D とソース S の間には、2 つの連続した PN 接合があります。ゲート・ソース間電圧 VGS=0 の場合、ドレイン・ソース間電圧 VDS を加えても常に逆バイアス状態の PN 接合が存在し、ドレイン・ソース間に導電チャネルが存在しません (電流が流れません)。 )。したがって、このときのドレイン電流ID=0となる。

このとき、ゲート・ソース間に順方向電圧が加わるとします。つまり、VGS>0の場合、ゲートがP型シリコン基板と整列した電界が、ゲート電極とシリコン基板の間のSiO2絶縁層に発生します。酸化物層は絶縁性であるため、ゲートに印加される電圧 VGS は電流を生成できません。酸化膜の両側にコンデンサが生成され、VGS等価回路はこのコンデンサ(コンデンサ)を充電します。そして、VGS がゲートの正の電圧に引き寄せられてゆっくり上昇すると、電界が発生します。多数の電子がこのコンデンサ (コンデンサ) の反対側に蓄積し、ドレインからソースへの N 型導電チャネルを作成します。 VGS が真空管のターンオン電圧 VT (一般に約 2V) を超えると、N チャンネル管がちょうど導通し始め、ドレイン電流 ID が生成されます。チャネルが最初にターンオン電圧を生成し始めるときのゲート・ソース間電圧をゲート・ソース電圧と呼びます。一般的にはVTと表現されます。

ゲート電圧VGSの大きさを制御することにより、電界の強弱が変化し、ドレイン電流IDの大きさを制御する効果が得られる。これは、電界を使用して電流を制御する MOSFET の重要な特徴でもあるため、電界効果トランジスタとも呼ばれます。

MOSFETの内部構造

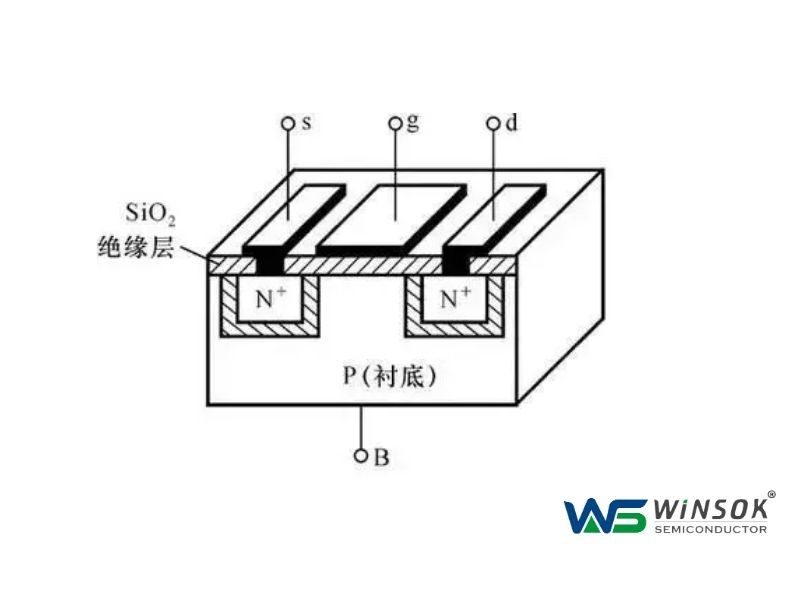

不純物濃度の低いP型シリコン基板上に、不純物濃度の高いN+領域を2つ作り、金属アルミニウムから2本の電極を引き出し、それぞれドレインdとソースsとして機能させます。次に、半導体表面を極めて薄い二酸化シリコン(SiO2)絶縁層で覆い、ドレイン・ソース間の絶縁層上にゲートgとなるアルミニウム電極を設置します。電極Bも基板上に引き出されており、NチャネルエンハンスメントモードMOSFETが形成されている。 Pチャネルエンハンスメント型MOSFETの内部構成も同様です。

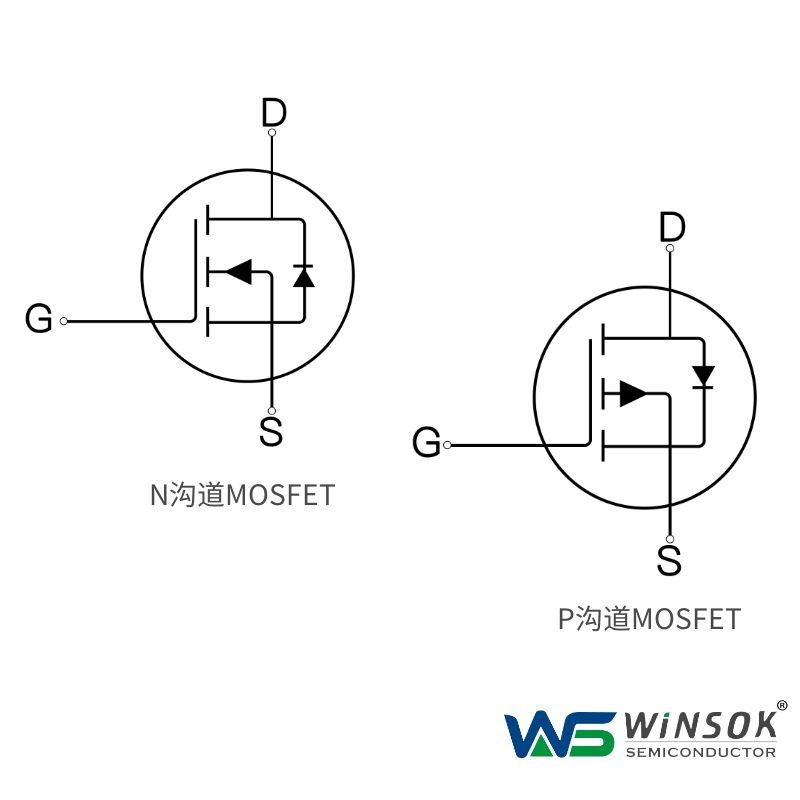

NチャネルMOSFETとPチャネルMOSFETの回路記号

上の図はMOSFETの回路記号を示しています。写真では、D はドレイン、S はソース、G はゲート、中央の矢印は基板を表します。矢印が内側を向いている場合は N チャネル MOSFET を示し、矢印が外側を向いている場合は P チャネル MOSFET を示します。

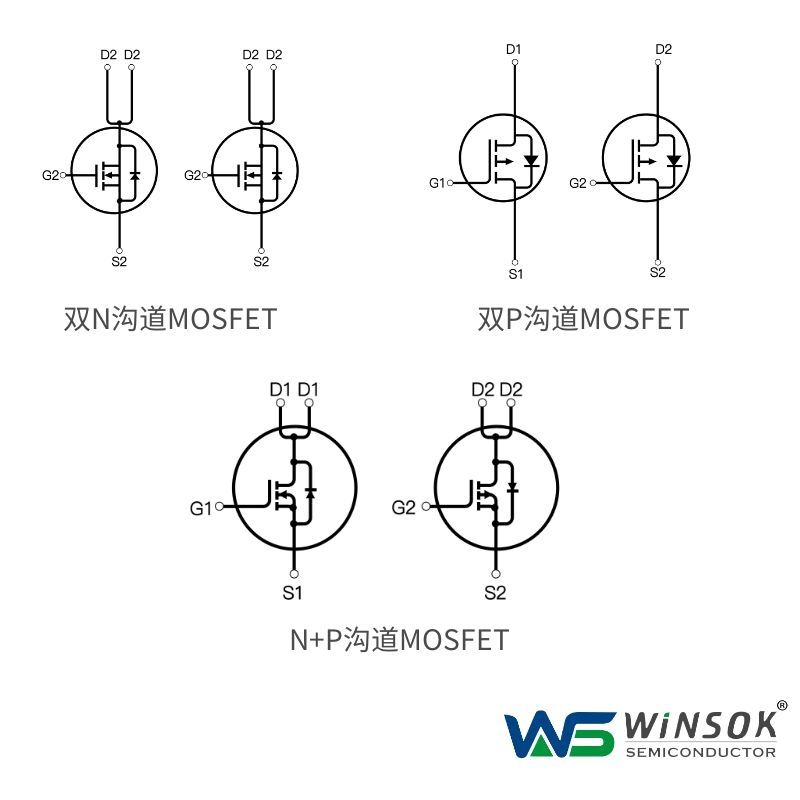

デュアル N チャネル MOSFET、デュアル P チャネル MOSFET、および N+P チャネル MOSFET の回路シンボル

実際、MOSFET の製造プロセス中、基板は工場から出荷される前にソースに接続されます。したがって、シンボル規則では、ドレインとソースを区別するために、基板を表す矢印シンボルもソースに接続する必要があります。 MOSFET で使用される電圧の極性は、従来のトランジスタと同様です。 N チャネルは NPN トランジスタに似ています。ドレインDは正極に接続され、ソースSは負極に接続される。ゲート G が正の電圧を持つと、導電チャネルが形成され、N チャネル MOSFET が動作し始めます。同様に、P チャネルは PNP トランジスタに似ています。ドレイン D は負極に接続され、ソース S は正極に接続され、ゲート G が負の電圧になると導電チャネルが形成され、P チャネル MOSFET が動作し始めます。

MOSFETのスイッチング損失原理

NMOSでもPMOSでも、ターンオン後には導通内部抵抗が発生するため、電流はこの内部抵抗にエネルギーを消費します。消費されるエネルギーのこの部分は、伝導消費と呼ばれます。導通内部抵抗が小さい MOSFET を選択すると、導通消費を効果的に削減できます。低電力 MOSFET の現在の内部抵抗は一般に数十ミリオーム程度ですが、数ミリオームの場合もあります。

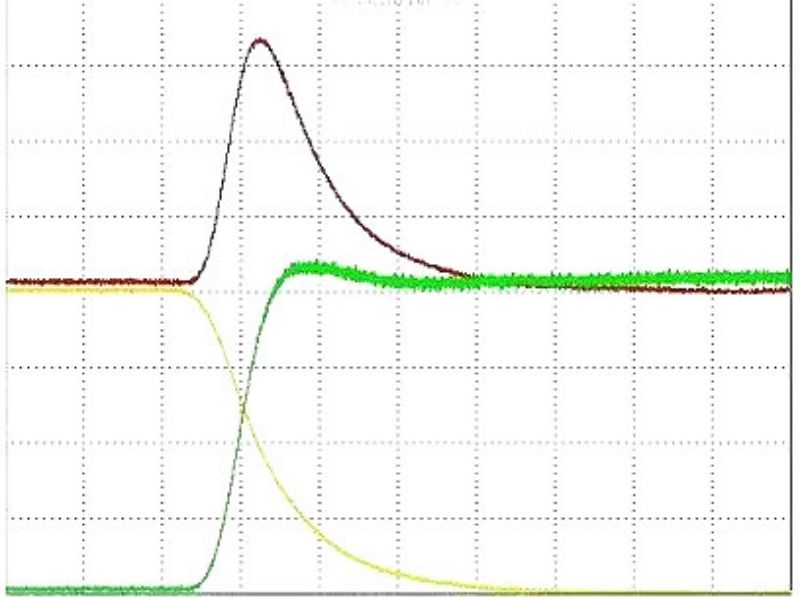

MOS のオンと終了は瞬時に実現してはなりません。 MOS の両側の電圧は実質的に減少し、MOS を流れる電流は増加します。この期間における MOSFET の損失は、電圧と電流の積、つまりスイッチング損失です。一般に、スイッチング損失は導通損失よりもはるかに大きく、スイッチング周波数が速いほど損失も大きくなります。

導通時の電圧と電流の積は非常に大きく、非常に大きな損失が発生します。スイッチング損失は 2 つの方法で低減できます。 1 つはスイッチング時間を短縮することで、各ターンオン時の損失を効果的に削減できます。もう 1 つはスイッチング周波数を下げることで、単位時間あたりのスイッチ数を減らすことができます。

以上、MOSFETの動作原理図とMOSFETの内部構造の解析について詳しく説明しました。 MOSFET についてさらに詳しく知りたい場合は、MOSFET の技術サポートを提供する OLUKEY にご相談ください。