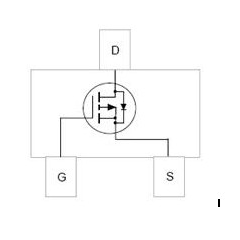

まずMOSFETの種類と構造ですが、MOSFETはFET(もう1つはJFET)で、エンハンスド型かデプレッション型、PチャネルかNチャネルの計4種類が製造できますが、実際に応用されるのはエンハンスドN型のみです。 - チャネル MOSFET とエンハンスド P チャネル MOSFET は、通常 NMOSFET と呼ばれ、PMOSFET は通常 NMOSFET と呼ばれ、PMOSFET はこれら 2 種類を指します。これら 2 種類の強化型 MOSFET では、オン抵抗が低く製造が容易なため、NMOSFET がより一般的に使用されます。したがって、NMOSFET はスイッチング電源やモーター駆動アプリケーションで一般的に使用されており、以下の紹介でも NMOSFET に焦点を当てます。寄生容量は 3 つのピン間に存在します。MOSFET、これは必要ではありませんが、製造プロセスの制限によるものです。寄生容量の存在により、ドライバ回路の設計または選択が少し難しくなります。ドレインとソースの間には寄生ダイオードが存在します。これはボディダイオードと呼ばれ、モーターなどの誘導負荷を駆動する場合に重要です。ちなみに、ボディダイオードは個々のMOSFETにのみ存在し、通常ICチップ内には存在しません。

今、MOSFET低電圧アプリケーションを駆動する場合、5V電源を使用する場合、今回は従来のトーテムポール構造を使用する場合、トランジスタによる電圧降下は約0.7Vとなり、最終的にゲートに追加される実際の電圧はわずかです。 4.3 V。現時点では、一定のリスクの存在を考慮して、MOSFET の公称ゲート電圧 4.5 V を選択します。 3Vなどの低電圧電源を使用する場合にも同様の問題が発生します。デュアル電圧は一部の制御回路で使用され、ロジック セクションでは一般的な 5V または 3.3V のデジタル電圧が使用され、電源セクションでは 12V 以上が使用されます。 2 つの電圧は共通のグランドを使用して接続されます。これにより、低電圧側が高電圧側の MOSFET を効果的に制御できる回路を使用する必要が生じますが、高電圧側の MOSFET は 1 と 2 で述べたのと同じ問題に直面することになります。

3 つのケースすべてにおいて、トーテムポール構造は出力要件を満たすことができず、多くの既製 MOSFET ドライバー IC にはゲート電圧制限構造が含まれていないようです。入力電圧は固定値ではなく、時間やその他の要因によって変化します。この変動により、PWM 回路によって MOSFET に供給される駆動電圧が不安定になります。 MOSFET を高いゲート電圧から安全にするために、多くの MOSFET にはゲート電圧の振幅を強制的に制限する電圧レギュレータが組み込まれています。この場合、電圧レギュレータよりも高い駆動電圧が供給されると、同時に大きな静的消費電力が発生します。単純に抵抗分圧器の原理を使用してゲート電圧を下げると、比較的高い消費電力が発生します。入力電圧、MOSFETゲート電圧が不十分で完全な導通が得られない場合、入力電圧が低下し、消費電力が増加します。

ここでは、NMOSFET ドライバ回路の比較的一般的な回路を簡単に分析してみます。Vl と Vh はローエンドとハイエンドの電源であり、2 つの電圧は同じであってもかまいませんが、Vl が Vh を超えてはなりません。 Q1 と Q2 は逆トーテム ポールを形成し、絶縁を実現すると同時に 2 つのドライバー チューブ Q3 と Q4 が同時に導通しないようにするために使用されます。 R2 と R3 は PWM 電圧を提供します。 R2 と R3 は PWM 電圧リファレンスを提供します。このリファレンスを変更することで、回路を PWM 信号波形が比較的急峻で直線的な位置で動作させることができます。 Q3 と Q4 は駆動電流を供給するために使用されます。オン時間のため、Q3 と Q4 は Vh および GND に対して最小の Vce 電圧降下にすぎません。この電圧降下は通常わずか 0.3V 程度であり、はるかに低くなります。 R5 と R6 はゲートに使用される帰還抵抗です。 R5 と R6 はゲート電圧をサンプリングするために使用される帰還抵抗です。ゲート電圧は Q5 を通過して、Vce のベースに強力な負帰還を生成します。 Q1 と Q2 により、ゲート電圧が有限値に制限されます。この値は R5 と R6 によって調整できます。最後に、R1 は Q3 と Q4 にベース電流の制限を提供し、R4 は MOSFET にゲート電流の制限を提供します。これは Q3Q4 の Ice の制限です。必要に応じて、加速コンデンサを R4 の上に並列に接続できます。