チャネルが存在すると D-FET は 0 ゲート バイアスになり、FET を導通させることができます。 E-FET はチャネルがない場合、ゲート バイアスが 0 になり、FET を導通できません。これら 2 種類の FET には、それぞれ独自の特徴と用途があります。一般に、高速、低電力回路における強化された FET は非常に価値があります。このデバイスが動作しているのは、ゲート バイアス vo の極性です。LTAGEとドレイン 電圧が同じであれば、回路設計においてより便利です。

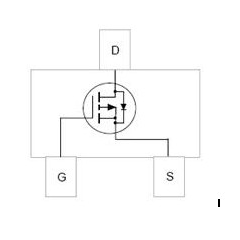

いわゆる強化とは、VGS = 0 のチューブがカットオフ状態であり、正しい VGS が加えられている場合、キャリアの大部分がゲートに引き付けられ、その領域内のキャリアが「強化」され、導電チャネルが形成されます。 nチャネルエンハンスドMOSFETは基本的に左右対称のトポロジーであり、SiO2膜絶縁層を形成した上にP型半導体を形成します。 P 型半導体上に SiO2 膜の絶縁層を生成し、次に高濃度にドープされた 2 つの N 型領域を拡散します。フォトリソグラフィー、N 型領域から電極を引き出します。1 つはドレイン D 用、もう 1 つはソース S 用です。アルミニウム金属の層が、ゲート G としてソースとドレインの間の絶縁層上にめっきされます。 VGS = 0 V の場合、ドレインとソースの間にダイオードが逆接続されているダイオードがかなりの数あり、DとSの間の電圧はDとSの間に電流を形成しません。DとSの間の電流は、印加された電圧によって形成されません。 。

ゲート電圧を加えると、0 < VGS < VGS(th) の場合、ゲートと基板の間に形成される容量電界によって、ゲート底部付近の P 型半導体のポリオンホールが下方向に反発され、マイナスイオンの薄い空乏層が現れます。同時にオリゴンも引き寄せられ表層に移動しますが、ドレインとソースを繋ぐ導電チャネルを形成するには数が限られており、ドレイン電流IDを形成するにはまだ不十分です。さらに増加する VGS、VGSのとき > VGS(th) (VGS(th)をターンオン電圧といいます)、このときゲート電圧が比較的強いため、ゲート底部付近のP型半導体表面層にはさらに多くの電圧が集まります。電子を利用して、トレンチ、ドレイン、通信源を形成できます。このときドレイン・ソース電圧を加えるとドレイン電流IDを形成することができます。ゲートの下に形成された導電チャネル内の電子は、P型半導体の極性が反対のキャリア正孔があるため、アンチタイプ層と呼ばれます。 VGS が増加し続けると、ID も増加し続けます。 VGS = 0V で ID = 0、ドレイン電流は VGS > VGS(th) になった後にのみ発生するため、このタイプの MOSFET はエンハンスメント MOSFET と呼ばれます。

ドレイン電流に対する VGS の制御関係は、伝達特性曲線と呼ばれる曲線 iD = f(VGS(th))|VDS=const と、伝達特性曲線の傾きの大きさ gm によって説明できます。ゲート・ソース電圧によるドレイン電流の制御を反映します。 gm の大きさは mA/V であるため、gm は相互コンダクタンスとも呼ばれます。